## **Cryogenic routing and interposer technologies**

Challenges and enabling technologies

**Flip Chip Integration** 3

Increasing complexity and number of qubits require scalable integration concepts

## **Challenges:**

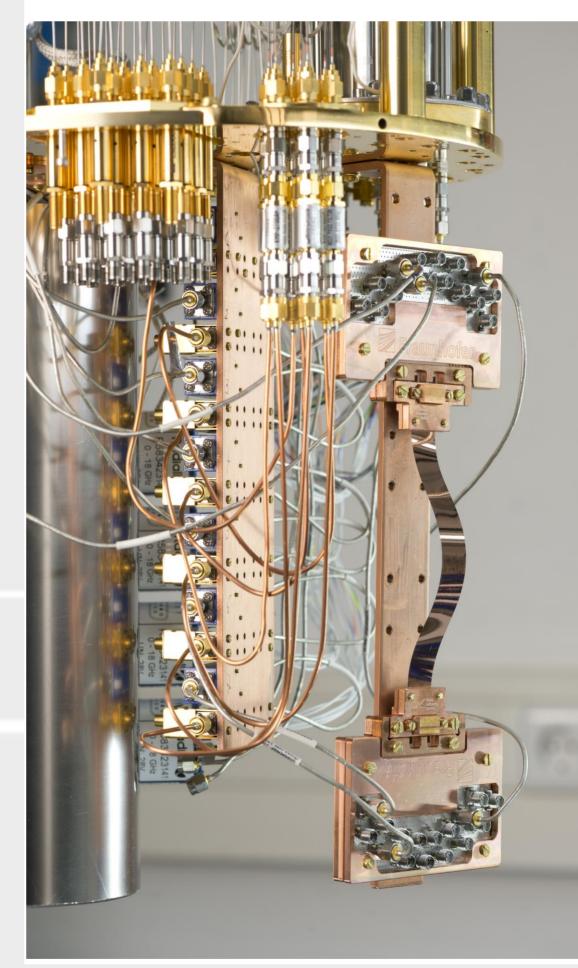

- Electromagnetic and thermal shielding, hardware architecture optimization

- High wiring and interconnection density

- Low-loss interposer substrates for integrating qubit chips and control ICs, minimizing signal loss to improve operational fidelity.

- Superconducting multilayer wiring and through-via of interposer substrates.

- Superconducting flip chip interconnects for scalable 3D integration and stacking

- Superconducting flex cables as connection to outside

- High-frequency-compatible cable routing with shielding

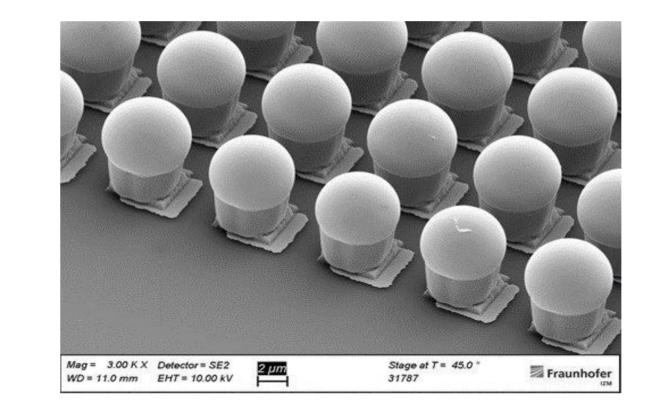

Flip chip interconnects must withstand thermo-mechanically large temperature changes into cryogenic temperature range. It should also provide superconductivity and fine pitch capability.

- Indium and indium/tin bumping best known for cryogenics

- Fine pitch capability down to 10 µm.

- Flip chip bonding temperature down to room temperature and fluxless reflow soldering

- Superconductive below 3.4K (In) and 5.4K (InSn)

Indium 10µm pitch:

- Homogeneous height

- Oxide removal

- Fluxless bonding

- High interconnect yield

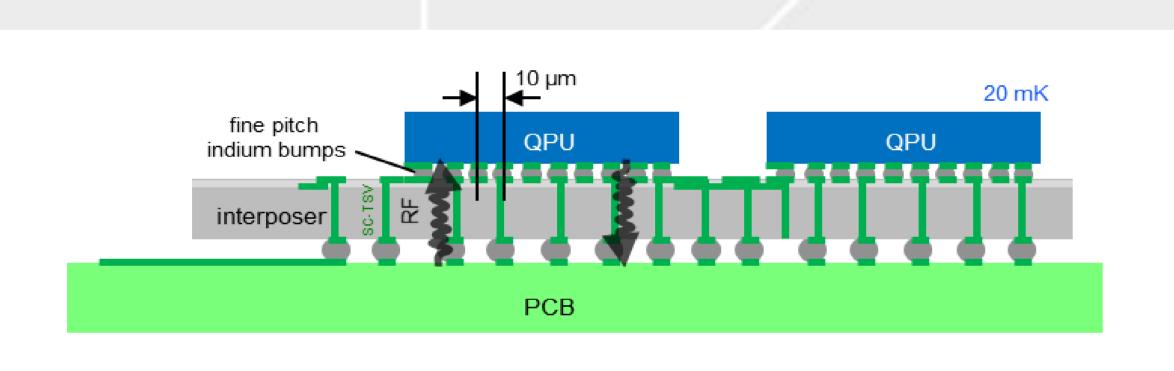

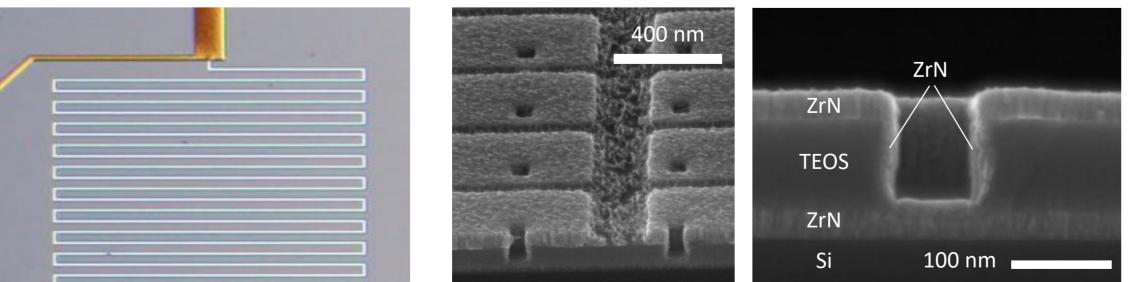

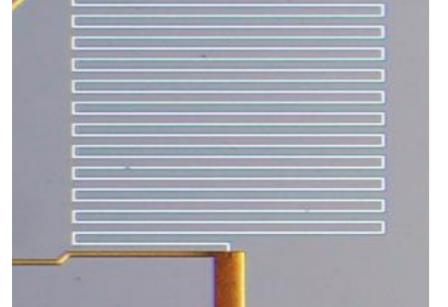

## **Interposer for 3D Integration** 2

Superconducting multilayer wiring and through-vias in interposer substrates are needed for 3D integration and stacking of QPUs and controller. This will require:

- Superconductive metal lines with high critical current density (e.g. Nb, NbN)

- Multilayer thinfilm redistribution layers (e.g. Nb, ZrN)

- Superconductive through vias (e.g. Nb)

Use of connections based on flexible foils and high-density PCB direct connectors

- Significantly line increased density (> 80 transmission lines per inch)

- Small cross section (100 µm thick)

High potential for miniaturization Low thermal conductivity

Fabricated role-to-role by process

- > simplified and cable fast manufacturing

- > increased overall uniformity

- > Arbitrary length

Niobium and niobium/ gold routing

SEM crosssection of two insulated ZrN layers with vertical interconnect for multilevel superconducting wiring

## Outlook 5

- Multilayer rewiring completely with superconductors

- Integration of technologies (bumping and rewiring)

- Reduction of line widths and spacing

- Reduction of bump pitch and increase in the number of contacts

- Thermal decoupling between interposer chips

SPONSORED BY THE