## **Enabling hybrid Al acceleration: HyDRA**

# Seamlessly Integrating the Power of Analog Computing in Hybrid (digital/analog) Al Accelerators

Elias Seon-Young Rhim, TileCore, Humboldt-University Berlin, seon-young.rhim@hu-berlin.de Max Johann Heyl, TileCore, Humboldt-University Berlin, max.heyl@hu-berlin.de Thomas Kämpfe, Fraunhofer IPMS, thomas.kaempfe@ipms.fraunhofer.de Markus Eppel, Fraunhofer IIS, markus.eppel@iis.fraunhofer.de David Borggreve, Ferdinand Pscheidl, Fraunhofer EMFT, ferdinand.pscheidl@emft.fraunhofer.de

#### Hybrid (D/A/D) AI Accelerators 1

#### Innovation 2

## The need of analog matrix computational power

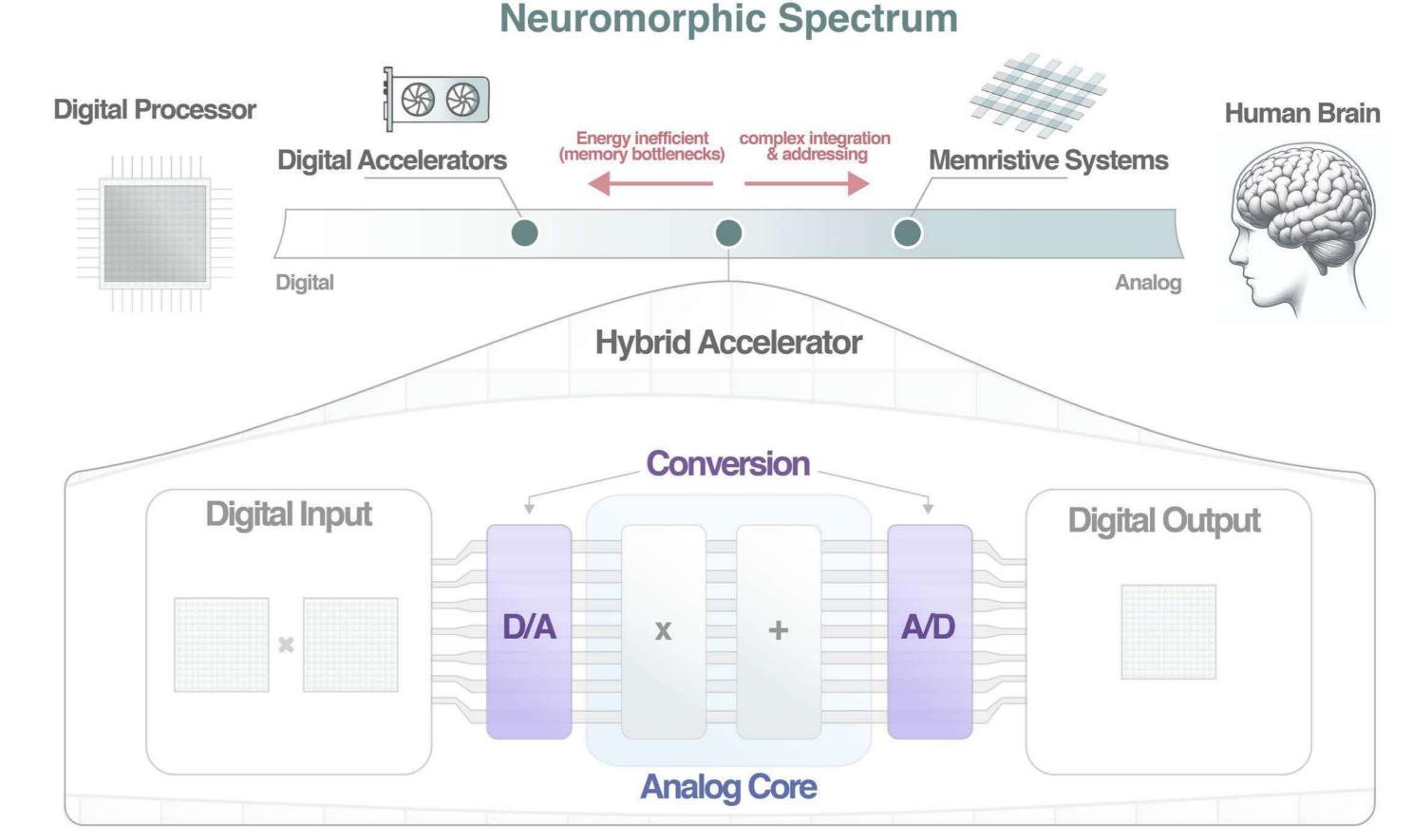

- Neuromorphic hardware aims to emulate AI at hardware level.

- Digital AI-Acceleration is energy inefficient at scale.

- Analog implementations promise energy efficient parallel computations.

## Challenge for analog neuromorphic hardware

The digital landscape demands conversion from

The hybrid position allows to harness both the benefits of the analog domain and the digital domain, but the conversion bottleneck needs to be addressed.

the analog to the digital domain.

Efficient conversion is key to seamlessly integrate analog hardware without

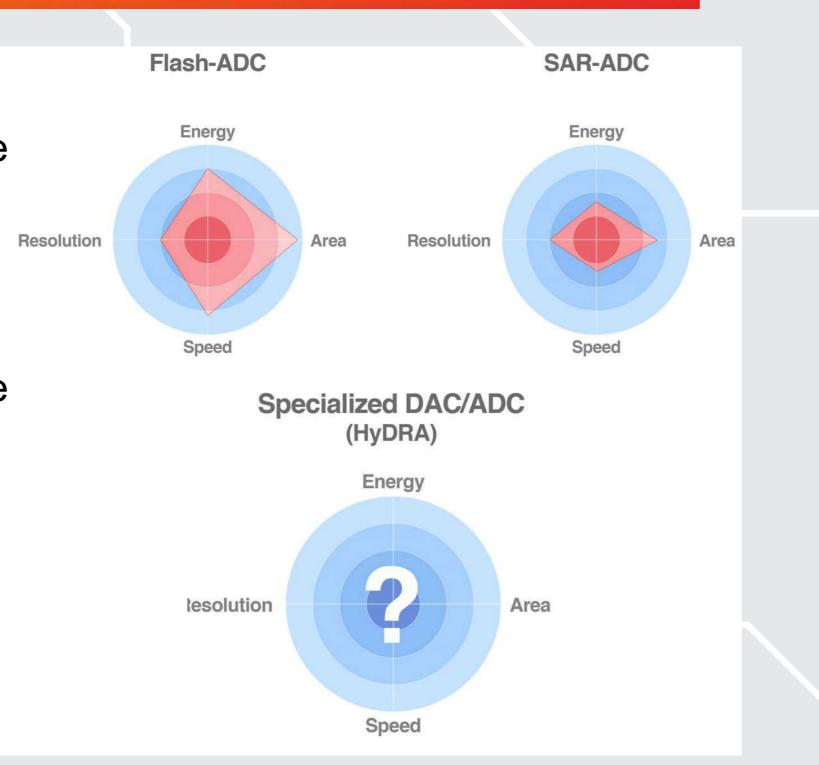

**DAC/ADCs** need to balance conversion speed, resolution and more.

## Why optimized conversion is key

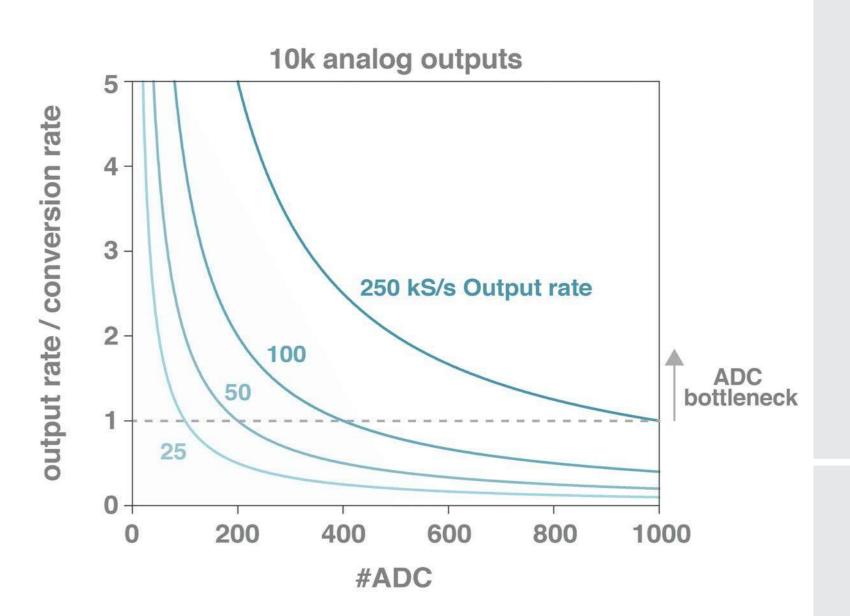

- Analog accelerators require many analog outputs.

- The large number of outputs strain the available conversion rate.

- Area- and energy efficient conversion (e.g. ADC arrays) is key to avoid bottlenecks.

#### Future performance profile & skills of the project partners 3

## Fraunhofer IPMS

Increasing the portfolio of design layouts and expertise in DAC solutions for AI accelerators and analog systems in general (e.g. photonics).

## Prospects

## Road to scaled hybrid acceleration

Optimized chip design for conversion solutions as building block.

### Fraunhofer EMFT & IIS

Increasing the portfolio of design layouts and expertise in ADC solutions for AI accelerators and neuromorphics.

## TileCore

Enabling hybrid AI accelerator solutions by combining conversion with in-house developed parallel analog cores.

- Combining these with analog core designs to design hybrid AI accelerators

- Industrially standardized foundry production of hybrid accelerators.

- Enabling energy efficient AI acceleration products.