Monolithisch integrierter Lasttrennschalter in JFET-basierter SiC-Technologie

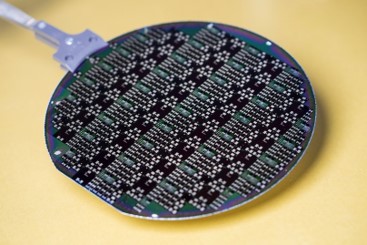

Kompletter 6‘‘ SiC Wafer mit hergestellten monolithisch integrierten Lasttrennschalter-Bauelementen.

„SiC-DCBreaker“ Chip nach dem Vereinzelungsprozess

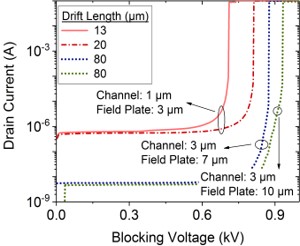

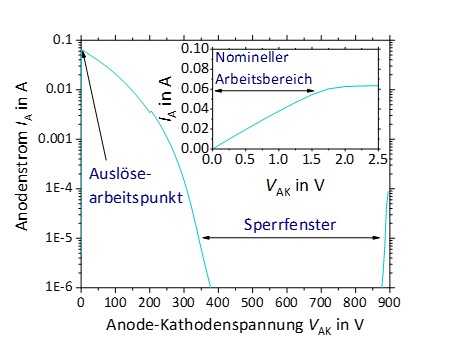

Gemessene Ausgangskennlinie einer Variante der hergestellten Lasttrenn-schalter–Bauelemente. Der Lasttrenn-schalter führt zu jedem Zeitpunkt den kompletten Laststrom. Nach dem Überschreiten des Auslösestroms wechselt das Bauelement von selbst umgehend in den Sperrbetrieb. Es ist keine externe Beschaltung notwendig. Einzige Voraussetzung ist, dass die Zwischenkreisspannung innerhalb des Sperrfensters liegt.

- Erste monolithisch integrierte Realisierung des »dualen Thyristors« in 4H-SiC JFET Technologie mit Potential für Großvolumenfertigung

- Selbstversorgte, selbstauslösende und selbsthaltende halbleiterbasierte Sicherung für DC-Netze und Anwendungen der E-Mobilität

- Die entwickelte Topologie ermöglicht Skalierbarkeit von Auslösestrom und Sperrspannung für anwendungsspezifische Anforderungen

Kooperationen:

- BMBF-gefördertes Projekt »SiC-DCBreaker« 03INT501BC

- Eigenforschung des Fraunhofer IISB

Veröffentlichungen:

- Boettcher N, Erlbacher T (2021): A Monolithically Integrated Circuit Breaker, in IEEE Electron Device Letters ( Volume: 42, Issue: 10, Oct. 2021). doi: 0.1109/LED.2021.3102935.

- Boettcher N, Erlbacher T (2020): Design Considerations on a Monolithically Integrated, Self Controlled and Regenerative 900 V SiC Circuit Breaker, in 2020 IEEE Workshop on Wide Bandgap Power Devices and Applications in Asia (WiPDA Asia). doi: 10.1109/WiPDAAsia49671.2020.9360279.

- Huerner A, et al. (2017): Monolithically Integrated Solid-State-Circuit-Breaker for High Power Applications, in ICSCRM, Materials Science Forum Vol. 897, 2017. doi: 10.4028/www.scientific.net/msf.897.661

Weiterführende Informationen

Fraunhofer-Verbund Mikroelektronik in Kooperation mit den Leibniz-Instituten FBH und IHP

Fraunhofer-Verbund Mikroelektronik in Kooperation mit den Leibniz-Instituten FBH und IHP